### General Description

The MAX1003 is a dual, 6-bit analog-to-digital converter (ADC) that combines high-speed, low-power operation with a user-selectable input range, an internal reference, and a clock oscillator. The dual parallel ADCs are designed to convert in-phase (I) and quadrature (Q) analog signals into two 6-bit, offset-binary-coded digital outputs at sampling rates up to 90Msps. The ability to directly interface with baseband I and Q signals makes the MAX1003 ideal for use in direct-broadcast satellite, VSAT, and QAM16 demodulation applications.

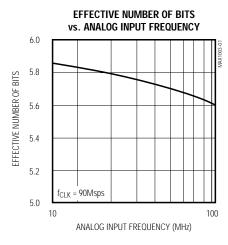

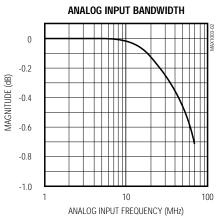

The MAX1003 input amplifiers feature true differential inputs, a -0.5dB analog bandwidth of 55MHz, and userprogrammable input full-scale ranges of 125mVp-p, 250mVp-p, or 500mVp-p. With an AC-coupled input signal, matching performance between input channels is typically better than 0.1dB gain, 1/4LSB offset, and 0.5° phase. Dynamic performance is 5.85 effective number of bits (ENOB) with a 20MHz analog input signal, or 5.7 ENOB with a 50MHz signal.

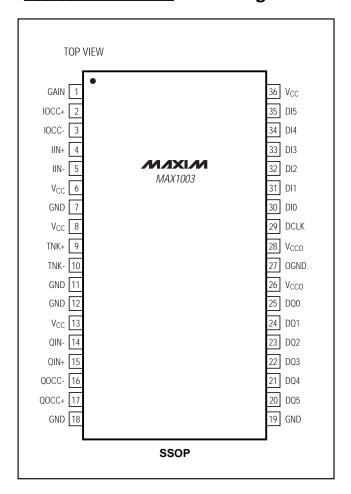

The MAX1003 operates with +5V analog and +3.3V digital supplies for easy interfacing to +3.3V-logic-compatible digital signal processors and microprocessors. It comes in a 36-pin SSOP package.

### **Applications**

Direct Broadcast Satellite (DBS) Receivers **VSAT** Receivers Wide Local Area Networks (WLANs) Cable Television Set-Top Boxes

**Features**

- ♦ Two Matched 6-Bit ADCs

- ♦ High Sampling Rate: 90Msps per ADC

- **♦ Low Power Dissipation: 350mW**

- **♦** Excellent Dynamic Performance: 5.85 ENOB with 20MHz Analog Input 5.7 ENOB with 50MHz Analog Input

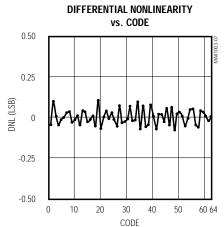

- ♦ ±1/4LSB INL and DNL (typ)

- ♦ Internal Bandgap Voltage Reference

- ♦ Internal Oscillator with Overdrive Capability

- ♦ 55MHz (-0.5dB) Bandwidth Input Amplifiers with **True Differential Inputs**

- ♦ User-Selectable Input Full-Scale Range (125mVp-p, 250mVp-p, or 500mVp-p)

- ♦ 1/4LSB Channel-to-Channel Offset Matching (typ)

- ◆ 0.1dB Gain and 0.5° Phase Matching (typ)

- **♦** Single-Ended or Differential Input Drive

- **♦** Flexible, 3.3V, CMOS-Compatible Digital Outputs

### Ordering Information

| PART       | TEMP. RANGE  | PIN-PACKAGE |  |

|------------|--------------|-------------|--|

| MAX1003CAX | 0°C to +70°C | 36 SSOP     |  |

Pin Configuration appears at end of data sheet.

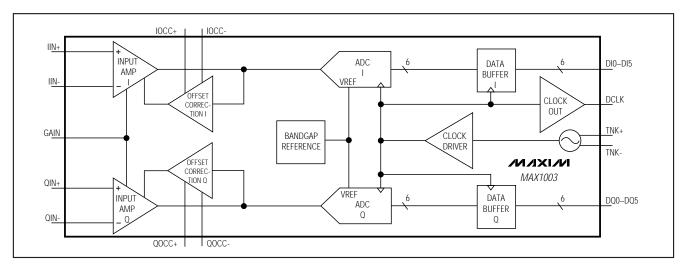

### Functional Diagram

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                 | 0.3V to 6.5V                     |

|----------------------------------------|----------------------------------|

| Vcco to OGND                           | 0.3V to 6.5V                     |

| GND to OGND                            | 0.3V to 0.3V                     |

| Digital and Clock Output Pins to OGND. | 0.3V to V <sub>CCO</sub> (10sec) |

| All Other Pins to GND                  | 0.3V to Vcc                      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ C | C)             |

|------------------------------------------------------|----------------|

| SSOP (derate 11.8mW/°C above +70°C                   | C)941mW        |

| Operating Temperature Range                          | 0°C to +70°C   |

| Storage Temperature Range                            | 65°C to +150°C |

| Lead Temperature (soldering, <10sec)                 | +300°C         |

|                                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +5V  $\pm$ 5%, V<sub>CCO</sub> = 3.3V  $\pm$ 300mV, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                             | SYMBOL           | CONDITIONS                                                                 | MIN     | TYP   | MAX    | UNITS |  |

|---------------------------------------|------------------|----------------------------------------------------------------------------|---------|-------|--------|-------|--|

| DC ACCURACY (Note 1)                  |                  |                                                                            |         |       |        |       |  |

| Resolution                            | RES              |                                                                            | 6       |       |        | Bits  |  |

| Integral Nonlinearity                 | INL              |                                                                            | -0.5    | ±0.25 | 0.5    | LSB   |  |

| Differential Nonlinearity             | DNL              | No missing codes over temperature                                          | -0.5    | ±0.25 | 0.5    | LSB   |  |

|                                       | V <sub>FSH</sub> | GAIN = V <sub>CC</sub> (high gain)                                         | 118.75  | 125   | 131.25 | mVp-p |  |

| Full-Scale Input Range                | VFSM             | GAIN = open (mid gain)                                                     | 237.5   | 250   | 262.5  |       |  |

|                                       | V <sub>FSL</sub> | GAIN = GND (low gain)                                                      | 475     | 500   | 525    |       |  |

| INVERTING AND NONINVERT               | ING ANALO        | G INPUTS                                                                   |         |       |        |       |  |

| Input Open-Circuit Voltage            | VAOC             |                                                                            | 2.25    | 2.35  | 2.45   | V     |  |

| Input Resistance                      | RIN              |                                                                            | 13      | 20    | 29     | kΩ    |  |

| Input Capacitance                     | CIN              | Guaranteed by design                                                       |         | 3     | 5      | рF    |  |

| Common-Mode Voltage Range             | V <sub>CM</sub>  | Other analog input driven with external source (Note 2)                    | 1.75    |       | 2.75   | V     |  |

| OSCILLATOR INPUTS                     |                  |                                                                            | l       |       |        |       |  |

| Oscillator Input Resistance           | Rosc             | Other oscillator input tied to V <sub>CC</sub> + 0.3V                      | 4.8     | 8     | 12.1   | kΩ    |  |

| DIGITAL OUTPUTS (DI0-DI5, I           | DQ0-DQ5)         |                                                                            |         |       |        |       |  |

| Digital Outputs Logic-High<br>Voltage | Voн              | ISOURCE = 50µA                                                             | 0.7Vcco |       |        | V     |  |

| Digital Outputs Logic-Low<br>Voltage  | V <sub>OL</sub>  | I <sub>SINK</sub> = 400μA                                                  |         |       | 0.5    | V     |  |

| POWER SUPPLY                          | <b>'</b>         |                                                                            | •       |       |        |       |  |

| Supply Current                        | Icc              |                                                                            |         | 63    | 104    | mA    |  |

| Power-Supply Rejection Ratio          | PSRR             | V <sub>CC</sub> = 4.75V to 5.25V (Note 3)                                  |         | -75   | -40    | dB    |  |

| Digital Outputs Supply Current        | Icco             | 20MHz, full-scale I and Q analog inputs,<br>C <sub>L</sub> = 15pF (Note 4) |         |       | 21     | mA    |  |

| Power Dissipation                     | PD               |                                                                            |         | 350   |        | mW    |  |

#### AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +5V  $\pm$ 5%, V<sub>CCO</sub> = 3.3V  $\pm$ 300mV, T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                         | SYMBOL            | CONDITIONS                                                                | MIN          | TYP         | MAX       | UNITS          |  |

|-------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------|--------------|-------------|-----------|----------------|--|

| <b>DYNAMIC PERFORMANCE</b> (Ga full scale, unless otherwise noted |                   | external 90MHz clock (Figure 7), V <sub>INI</sub> = V <sub>INQ</sub> =    | = 20MHz sine | e, amplitud | le -1dB k | pelow          |  |

| Maximum Sample Rate                                               | f <sub>MAX</sub>  |                                                                           | 90           |             |           | Msps           |  |

| Analog Input -0.5dB Bandwidth                                     | BW                | GAIN = GND, open, VCC                                                     |              | 55          |           | MHz            |  |

|                                                                   |                   | GAIN = open (mid gain)                                                    | 5.6          | 5.85        |           | Bits           |  |

| Effective Number of Bits                                          | ENOB <sub>M</sub> | GAIN = open (mid gain), f <sub>IN</sub> = 50MHz,<br>-1dB below full scale |              | 5.7         |           |                |  |

|                                                                   | ENOBH             | GAIN = V <sub>CC</sub> (high gain)                                        |              | 5.8         |           |                |  |

|                                                                   | ENOBL             | GAIN = GND (low gain)                                                     |              | 5.85        |           |                |  |

| Signal-to-Noise plus Distortion Ratio                             | SINAD             | GAIN = open (mid gain)                                                    | 35.5         | 37          |           | dB             |  |

| La controlled at (NICtor E)                                       | OFF               | I channel                                                                 | -0.5         |             | 0.5       | LSB            |  |

| Input Offset (Note 5)                                             |                   | Q channel                                                                 | -0.5         |             | 0.5       |                |  |

| Crosstalk Between ADCs                                            | XTLK              |                                                                           |              | -55         |           | dB             |  |

| Offset Mismatch Between ADCs                                      | OMM               | (Note 5)                                                                  | -0.5         | ±0.25       | 0.5       | LSB            |  |

| Amplitude Match Between ADCs                                      | AM                |                                                                           | -0.2         | ±0.1        | 0.2       | dB             |  |

| Phase Match Between ADCs                                          | PM                |                                                                           | -2           | ±0.5        | 2         | degrees        |  |

| TIMING CHARACTERISTICS (                                          | ata outputs       | $: R_L = 1M\Omega, C_L = 15pF)$                                           |              |             |           | I              |  |

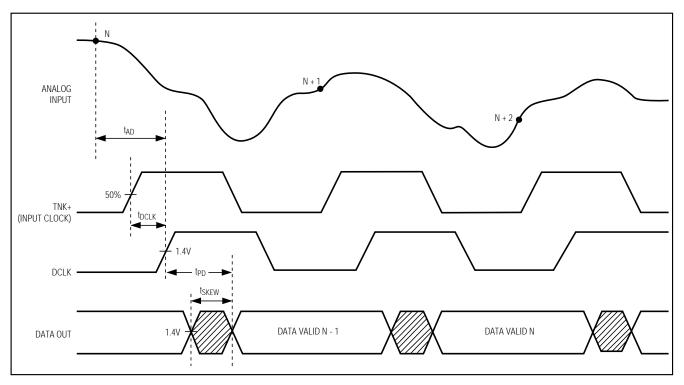

| Clock to Data Propagation<br>Delay                                | tpD               | (Note 6)                                                                  |              | 3.6         |           | ns             |  |

| Data Valid Skew                                                   | tskew             | (Note 6)                                                                  |              | 1.5         |           | ns             |  |

| Input to DCLK Delay                                               | tDCLK             | TNK+ to DCLK (Note 6)                                                     |              | 5.3         |           | ns             |  |

| Aperture Delay                                                    | tad               | Figure 8                                                                  |              | 7.5         |           | ns             |  |

| Pipeline Delay                                                    | PD                | Figure 8                                                                  |              | 1           |           | clock<br>cycle |  |

- Note 1: Best-fit straight-line linearity method.

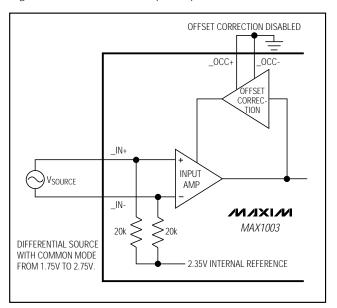

- Note 2: A typical application will AC couple the analog input to the DC bias level present at the analog inputs (typically 2.35V). However, it is also possible to DC couple the analog input (using differential or single-ended drive) within this common-mode input range (Figures 4 and 5).

- **Note 3:** PSRR is defined as the change in the mid-gain full-scale range as a function of the variation in V<sub>CC</sub> supply voltage, expressed in decibels.

- **Note 4:** The current in the V<sub>CCO</sub> supply is a strong function of the capacitive loading on the digital outputs. To minimize supply transients and achieve optimal dynamic performance, reduce the capacitive-loading effects by keeping line lengths on the digital outputs to a minimum.

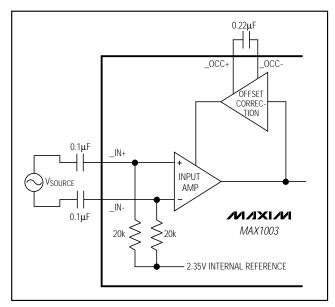

- Note 5: Offset-correction compensation enabled, 0.22µF at Q and I compensation inputs (Figures 2 and 3).

- Note 6: tpD and tsKew are measured from the 1.4V level of the output clock, to the 1.4V level of either the rising or falling edge of a data bit. tDCLK is measured from the 50% level of the clock-overdrive signal on TNK+ to the 1.4V level of DCLK. The capacitive load on the outputs is 15pF.

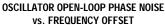

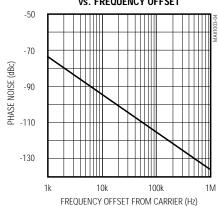

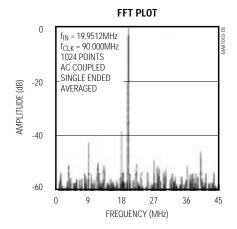

### Typical Operating Characteristics

$(V_{CC} = +5V \pm 5\%, V_{CCO} = 3.3V \pm 300 mV, f_{CLK} = 90 Msps, GAIN = open (midgain) MAX1003 evaluation kit, T_A = +25°C, unless otherwise noted.)$

CODE

60 64

INTEGRAL NONLINEARITY

-0.50

10 20 30 40 50

#### Pin Description

| PIN                  | NAME    | FUNCTION                                                                                                                                |  |  |

|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                    | GAIN    | Gain-Select Input. Sets input full-scale range: 125/250/500mVp-p (Table 1).                                                             |  |  |

| 2                    | IOCC+   | Positive I-Channel Offset-Correction Compensation. Connect a $0.22\mu F$ capacitor for AC-coupled inputs. Ground for DC-coupled inputs. |  |  |

| 3                    | IOCC-   | Negative I-Channel Offset-Correction Compensation. Connect a 0.22µF capacitor for AC-coupled inputs. Ground for DC-coupled inputs.      |  |  |

| 4                    | IIN+    | I-Channel Noninverting Analog Input                                                                                                     |  |  |

| 5                    | IIN-    | I-Channel Inverting Analog Input                                                                                                        |  |  |

| 6                    | Vcc     | $+5V$ $\pm5\%$ Supply. Bypass with a 0.01 $\mu$ F capacitor to GND (pin 7).                                                             |  |  |

| 7, 11, 12,<br>18, 19 | GND     | Analog Ground                                                                                                                           |  |  |

| 8                    | Vcc     | +5V ±5% Supply. Bypass with a 0.01μF capacitor to GND (pin 11).                                                                         |  |  |

| 9                    | TNK+    | Positive Oscillator/Clock Input                                                                                                         |  |  |

| 10                   | TNK-    | Negative Oscillator/Clock Input                                                                                                         |  |  |

| 13                   | Vcc     | +5V ±5% Supply. Bypass with a 0.01μF capacitor to GND (pin 12).                                                                         |  |  |

| 14                   | QIN-    | Q-Channel Inverting Analog Input                                                                                                        |  |  |

| 15                   | QIN+    | Q-Channel Noninverting Analog Input                                                                                                     |  |  |

| 16                   | QOCC-   | Negative Q-Channel Offset-Correction Compensation. Connect a 0.22µF capacitor for AC-coupled inputs. Ground for DC-coupled inputs.      |  |  |

| 17                   | QOCC+   | Positive Q-Channel Offset-Correction Compensation. Connect a 0.22µF capacitor for AC-coupled inputs. Ground for DC-coupled inputs.      |  |  |

| 20-25                | DQ5-DQ0 | Q-Channel Digital Outputs 0–5. DQ5 is the most significant bit (MSB).                                                                   |  |  |

| 26, 28               | Vcco    | Digital Output Supply, +3.3V ±300mV. Bypass each with a 47pF capacitor to OGND (pin 27).                                                |  |  |

| 27                   | OGND    | Digital Output Ground                                                                                                                   |  |  |

| 29                   | DCLK    | Digital Clock Output. Frames the output data.                                                                                           |  |  |

| 30–35                | DI0-DI5 | I-Channel Digital Outputs 0–5. DI5 is the most significant bit (MSB).                                                                   |  |  |

| 36                   | Vcc     | +5V ±5% Supply. Bypass with a 0.01μF capacitor to GND (pin 19).                                                                         |  |  |

|                      |         |                                                                                                                                         |  |  |

### Detailed Description

#### **Converter Operation**

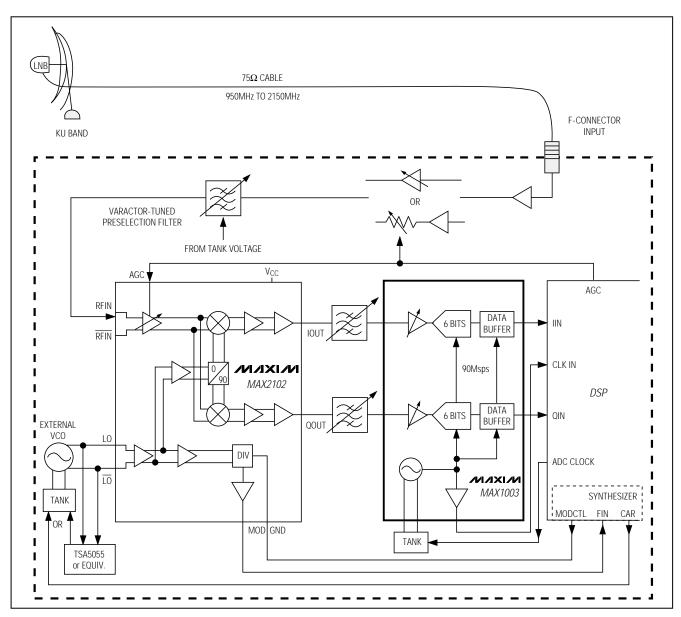

The MAX1003 contains two 6-bit analog-to-digital converters (ADCs), a buffered voltage reference, and oscillator circuitry. The ADCs use a flash conversion technique to convert an analog input signal into a 6-bit parallel digital output code. The MAX1003's unique design includes 63 fully differential comparators and a proprietary encoding scheme that ensures no more than 1LSB dynamic encoding error. The control logic interfaces easily to most digital signal processors (DSPs) and microprocessors ( $\mu$ Ps) with +3.3V CMOScompatible logic interfaces. Figure 1 shows the MAX1003 in a typical application.

#### **Programmable Input Amplifiers**

The MAX1003 has two (I and Q) programmable-gain input amplifiers with a -0.5dB bandwidth of 55MHz and true differential inputs. To maximize performance in high-speed systems, each amplifier has less than 5pF of input capacitance. The input amplifier gain is programmed, via the GAIN pin, to provide three possible input full-scale ranges (FSRs) as shown in Table 1.

**Table 1. Input Amplifier Programming**

| GAIN | INPUT FULL-SCALE RANGE<br>(mVp-p) |

|------|-----------------------------------|

| GND  | 500                               |

| Open | 250                               |

| Vcc  | 125                               |

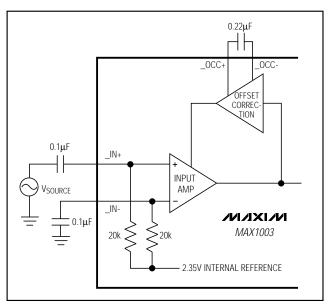

Single-ended and differential AC-coupled input circuits are shown in Figures 2 and 3. Each of the amplifier inputs is internally biased to a 2.35V reference through a  $20k\Omega$  resistor, eliminating external DC bias circuits. A series  $0.1\mu F$  capacitor is required at each amplifier input for AC-coupled signals.

When operating with AC-coupled inputs, the input amplifiers' DC offset voltage is nulled to within  $\pm 1/2LSB$  by an on-chip offset-correction amplifier. An external

compensation capacitor is required to set the dominant pole of the offset-correction amplifier's frequency response (Figures 2 and 3). The compensation capacitor will determine the low-frequency corner of the analog input response according to the following formula:

$$f_C = 1 / (0.1 \times C)$$

where C is the value of the compensation capacitor in  $\mu F,$  and  $f_C$  is the corner frequency in Hz.

Figure 1. Commercial Satellite Receiver System

Figure 2. Single-Ended AC-Coupled Input

Figure 4. Single-Ended DC-Coupled Input

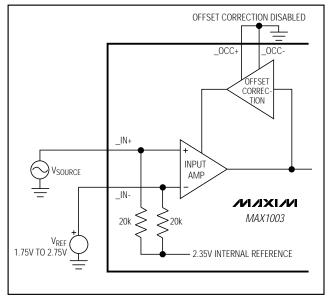

For applications where a DC component of the input signal is present, Figures 4 and 5 show single-ended and differential DC-coupled input circuits. The amplifiers' input common-mode voltage range extends from 1.75V to 2.75V. To prevent attenuation of the input signal's DC component in this mode, disable the offset-correction amplifier by grounding the \_OCC+ and \_OCC- pins for the I and Q blocks (Figures 4 and 5).

Figure 3. Differential AC-Coupled Input

Figure 5. Differential DC-Coupled Input

#### **ADCs**

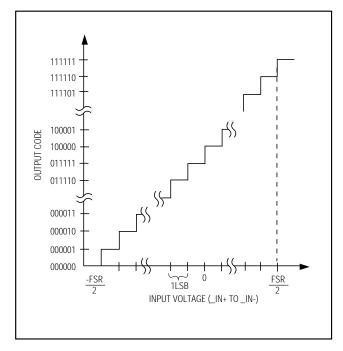

The I and Q ADC blocks receive the analog signals from the respective I and Q input amplifiers. The ADCs use flash conversion with 63 fully differential comparators to digitize the analog input signal into a 6-bit output in offset binary format.

The MAX1003 features a proprietary encoding scheme that ensures no more than 1LSB dynamic encoding error. Dynamic encoding errors resulting from metastable states may occur when the analog input voltage, at the time the sample is taken, falls close to the decision point for any one of the input comparators. The resulting output code for typical converters can be incorrect, including false full- or zero-scale outputs. The MAX1003's unique design reduces the magnitude of this type of error to 1LSB.

#### Internal Voltage Reference

An internal buffered bandgap reference is included on the MAX1003 to drive the ADCs' reference ladders. The on-chip reference and buffer eliminate any external (high-impedance) connections to the reference ladder, minimizing the potential for noise coupling from external circuitry while ensuring that the voltage reference, input amplifier, and reference ladder track well with variations of temperature and power supplies.

#### **Oscillator Circuit**

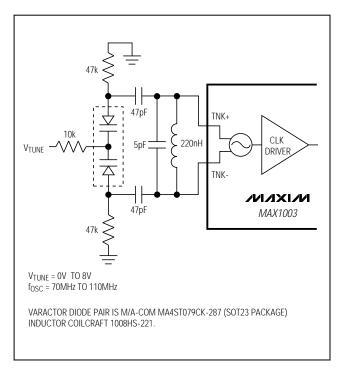

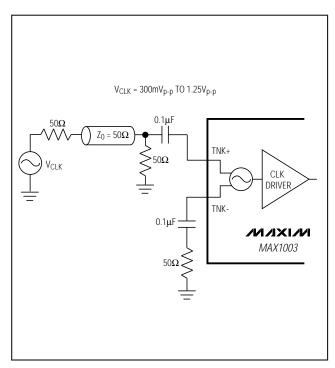

The MAX1003 includes a differential oscillator, which is controlled by an external parallel resonant (tank) network as shown in Figure 6. Alternatively, the oscillator may be overdriven with an external clock source as shown in Figure 7.

#### Internal Clock Operation (Tank)

If the tank circuit is used, the resonant inductor should have a sufficiently high Q and a self-resonant frequency (SRF) of at least twice the intended oscillator frequency. Coilcraft's 1008HS-221, with an SRF of 700MHz and a Q of 45, works well for this application. Generate different clock frequency ranges by adjusting varactor and tank elements.

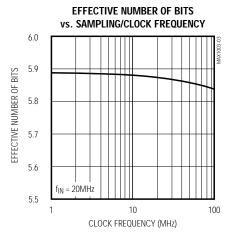

An internal clock-driver buffer is included to provide sharp clock edges to the internal flash comparators. The buffer ensures that the comparators are simultaneously clocked, maximizing the ADCs' effective number of bits (ENOB) performance.

Figure 6. Tank Resonator Oscillator

Figure 7. External Clock Drive Circuit

Figure 8. MAX1003 Timing Diagram

#### External Clock Operation

To accommodate designs that use an external clock, the MAX1003's internal oscillator can be overdriven by an external clock source as shown in Figure 7. The external clock source should be a sinusoid to minimize clock phase noise and jitter, which can degrade the ADCs' ENOB performance. AC couple the clock source (recommended voltage level is approximately 1Vp-p) to the oscillator inputs as shown in Figure 7.

#### **Output Data Format**

The conversion results are output on a dual, 6-bit-wide data bus. Data is latched into the ADC output latch following a pipeline delay of one clock cycle, as shown in Figure 8. Output data is clocked out of the respective ADC's data output pins (D\_0 through D\_5) on the rising edge of the clock output (DCLK), with a DCLK-to-data propagation delay (tpD) of 3.6ns. The MAX1003 outputs are +3.3V CMOS-logic compatible.

#### **Transfer Function**

Figure 9 shows the MAX1003's nominal transfer function. Output coding is offset binary with 1LSB = FSR / 63.

Figure 9. Ideal Transfer Function

### \_Applications Information

The MAX1003 is designed with separate analog and digital power-supply and ground connections to isolate high-current digital noise spikes from the more sensitive analog circuitry. The high-current digital output ground (OGND) and analog ground (GND) should be at the same DC level, connected at only one location on the board. This will provide best noise immunity and improved conversion accuracy. Use of separate ground planes is strongly recommended.

The entire board needs good DC bypassing for both analog and digital supplies. Place the power-supply bypass capacitors close to where the power is routed onto the board, i.e., close to the connector. 10µF electrolytic capacitors with low-ESR ratings are recommended. For best effective bits performance, minimize capacitive loading at the digital outputs. Keep the digital output traces as short as possible.

The MAX1003 requires a +5V  $\pm$ 5% power supply for the analog supply (V<sub>CC</sub>) and a +3.3V  $\pm$ 300mV power supply connected to V<sub>CCO</sub> for the logic outputs. Bypass each of the V<sub>CC</sub> supply pins to its respective GND with high-quality ceramic capacitors located as close to the package as possible (Table 2). Consult the evaluation kit manual for a suggested layout and bypassing scheme.

Table 2. Bypassing

| SUPPLY<br>FUNCTION | V <sub>CC</sub> /<br>V <sub>CCO</sub> | BYPASS<br>TO<br>GND/<br>OGND | CAPACITOR<br>VALUE |

|--------------------|---------------------------------------|------------------------------|--------------------|

| Analog Inputs      | 6                                     | 7                            | 0.01µF             |

| Oscillator/Clock   | 8                                     | 11                           | 0.01µF             |

| Converter          | 13                                    | 12                           | 0.01µF             |

| Digital Q-Output   | 26                                    | 27                           | 47pF               |

| Digital I-Output   | 28                                    | 27                           | 47pF               |

| Buffer             | 36                                    | 19                           | 0.01µF             |

### \_Dynamic Performance

Signal-to-noise and distortion (SINAD) is the ratio of the fundamental input frequency's RMS amplitude to all other ADC output signals. The output spectrum is limited to frequencies above DC and below one-half the ADC sample rate.

The theoretical minimum analog-to-digital noise is caused by quantization error, and results directly from the ADC's resolution: SNR = (6.02N + 1.76)dB, where N is the number of bits of resolution. Therefore, a perfect 6-bit ADC can do no better than 38dB.

The FFT Plot (see *Typical Operating Characteristics*) shows the result of sampling a pure 20MHz sinusoid at a 90MHz clock rate. This FFT plot of the output shows the output level in various spectral bands. The plot has been averaged to reduce the quantization noise floor and reveal the low-amplitude spurs. This emphasizes the excellent spurious-free dynamic range of the MAX1003.

The effective resolution (or effective number of bits) the ADC provides can be measured by transposing the equation that converts resolution to SINAD: N = (SINAD - 1.76) / 6.02 (see *Typical Operating Characteristics*).

### \_Pin Configuration

\_\_\_\_Chip Information

TRANSISTOR COUNT: 6097

#### INCHES MILLIMETERS MIN MAXMIN MAX 0.104 2.65 0.094 A1 0.004 0.011 0.10 0.28 0.011 0.017 0.30 0.44 0.009 | 0.012 0.23 0.32 0.0315 0.80 0.292 0.298 7.42 7.57 0.398 0.416 10.10 10.57 Н 0.020 0.035 0.51 0.89 MILLIMETERS INCHES MIN MAX MIN MAX D 0.604 0.610 15.34 15.49 36 D 0.702 0.708 17.83 17.98 44 Α1

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

NOTES:

.102mm (.004")

5. N = NUMBER OF PINS

D&E DO NOT INCLUDE MOLD FLASH

MOLD FLASH OR PROTRUSIONS NOT TO EXCEED .15mm (.006")

LEADS TO BE COPLANAR WITHIN

CONTROLLING DIMENSION: MILLIMETER

PACKAGE DUTLINE, SSDP, 36/44L

APPROVAL | DOCUMENT CONTROL NO.

21-0040

Package Information